# NSITEXE NS31A User Manual

NSITEXE, Inc.

NRV31210004-00-E Revision 3.0.0

# Index

| About This Document                       |    |

|-------------------------------------------|----|

| Notices and Disclaimers                   |    |

| Target Design                             |    |

| Relevant Documents                        |    |

| Reference Documents                       |    |

| Abbreviations                             | 4  |

| 1. NSITEXE NS31A Core Overview            | 5  |

| 1.1. Features                             | 5  |

| 1.2. Function Block Diagram               |    |

| 2. Memory Map                             |    |

| 2.1. Address Map                          |    |

| 2.1.1. Address Regions                    |    |

| 2.1.2. Bus access routing                 |    |

| 2.2. RAM                                  |    |

| 2.2.1. Features                           | 19 |

| 2.3. Cache Control                        |    |

| 2.3.1. Features                           |    |

| 2.3.2. Registers                          |    |

| 2.3.3. Operations                         | 20 |

| 3. NS31A Core                             | 23 |

| 3.1. Overview                             | 23 |

| 3.1.1. Execution Control Part             | 23 |

| 3.1.2. Hardware Thread                    | 23 |

| 3.2. Physical Memory Protection (PMP)     | 24 |

| 3.2.1. Features                           | 24 |

| 3.2.2. Registers                          | 26 |

| 3.3. Operating States                     | 27 |

| 3.3.1. System-level states                | 27 |

| 3.3.2. Core-level states                  |    |

| 3.3.3. Hart-level states.                 |    |

| 3.4. Exceptions                           |    |

| 3.4.1. NS31A unique exception list        |    |

| 3.4.2. Exception priority                 |    |

| 3.5. Interrupts                           | 40 |

| 3.5.1. Features                           | 40 |

| 3.5.2. Software interrupt                 | 40 |

| 3.5.3. Timer interrupt                    | 40 |

| 3.5.4. External interrupt                 | 41 |

| 3.5.5. Error Interrupt                    | 41 |

| 3.5.6. Non-maskable interrupt (NMI)       | 41 |

| 3.6. Privileged ISA                       | 42 |

| 3.7. Control and Status Registers         | 43 |

| 3.7.1. CSR Address Map                    | 43 |

| 3.7.2. NS31A CSRs                         | 43 |

| 3.7.3. Hardware Performance Monitor (HPM) |    |

| 3.8. Memory Mapped Control Registers      | 91 |

| 3.8.1. Memory Mapped Control Register     | 91 |

| 3.8.2. Hart Context Register              | 93 |

| 3.8.3. Register descriptions              | 94 |

| 3.9. Instruction Set                      |    |

| 3.9.1. Base Integer Instruction Set (RV32I, RV32E)                           | 112 |

|------------------------------------------------------------------------------|-----|

| 3.9.2. Instruction-Fetch Fence (Zifencei)                                    | 113 |

| 3.9.3. Integer Multiplication and Division (RV32M)                           | 113 |

| 3.9.4. Atomic Instructions (RV32A)                                           | 113 |

| 3.9.5. Control and Status Register (CSR) Instructions (Zicsr)                | 113 |

| 3.9.6. Single-Precision Floating Point (RV32F)                               | 113 |

| 3.9.7. Bit manipulation extension (RV32B)                                    | 116 |

| 3.9.8. Compressed Instructions (RV32C)                                       | 117 |

| 3.10. Mutual Exclusion                                                       |     |

| 3.10.1. Atomic Memory Operation (AMO)                                        | 118 |

| 3.10.2. Load-Reserved/Store-Conditional Instructions (LR/SC)                 | 120 |

| 3.10.3. Exclusive access support by an external AXI master                   |     |

| 3.10.4. Exclusive monitor                                                    |     |

| 3.11. Branch Prediction                                                      |     |

| 3.11.1. BTB entry Test interface                                             |     |

| 3.12. Usage Notes                                                            |     |

| 3.12.1. Memory Consistency Model.                                            |     |

| 3.12.2. Amount of look-ahead in speculative access to a memory               |     |

| 3.12.3. Behavior if an error occurs due to memory access                     |     |

| 3.12.4. Behavior if the FENCE.I instruction is executed                      |     |

| 3.12.5. Behavior when PMP setting is changed                                 |     |

| 3.12.6. Minimum region granularity of instruction fetch for PMP              |     |

| 3.12.7. Optimization of the integer multiplier and divider                   |     |

| 4. Bus Interface                                                             |     |

| 4.1. Interfaces                                                              |     |

| 4.1.1. System Bus Master                                                     |     |

| 4.1.2. External Peripheral Bus Master 4.1.3. Front Port Bus Slave            |     |

| 4.1.4. Instruction Bus Master Interface.                                     |     |

| 4.1.5. Data Bus Master Interface                                             |     |

| 4.1.6. Peripheral Bus Slave Interface                                        |     |

| 4.2. Features.                                                               |     |

| 4.2.1. Sideband Information                                                  |     |

| 5. System Control                                                            |     |

| 5.1. Clock                                                                   |     |

| 5.2. Reset                                                                   |     |

| 5.2.1. Power-on Reset                                                        |     |

| 5.2.2. System Reset                                                          |     |

| 5.2.3. JTAG Reset                                                            |     |

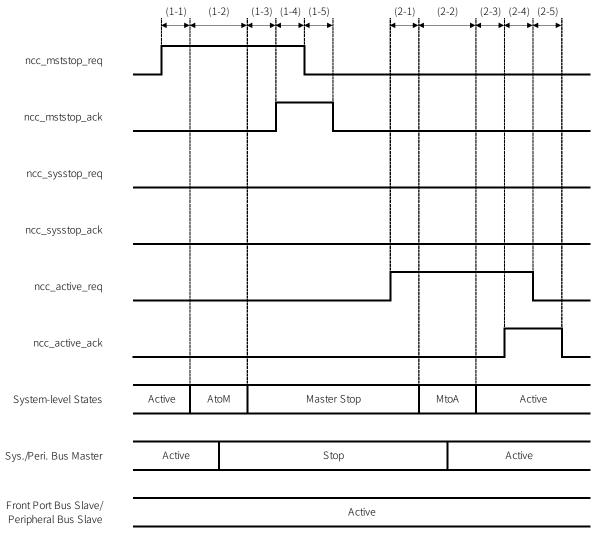

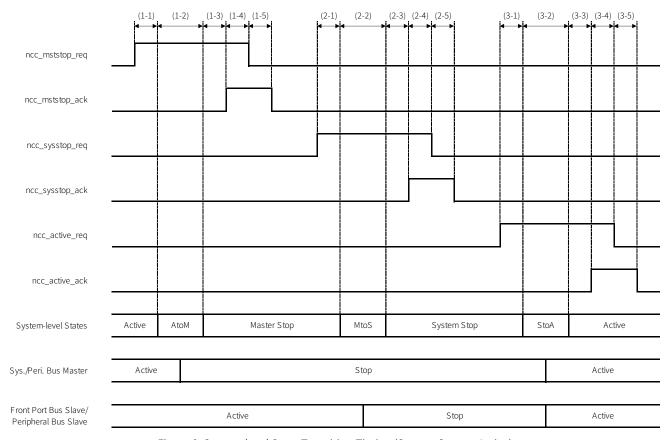

| 5.3. System-level State Control                                              | 143 |

| 5.3.1. Master Stop to Active                                                 | 144 |

| 5.3.2. System Stop to Active                                                 | 146 |

| 5.3.3. System Stop to System Reset                                           | 148 |

| 5.3.4. Debug Logic Stop                                                      | 149 |

| 6. Core Management Unit (CMU)                                                | 150 |

| 6.1. Features                                                                |     |

| 6.1.1. Clock Control                                                         | 150 |

| 6.1.2. Reset Control                                                         | 150 |

| 6.1.3. States Control                                                        |     |

|                                                                              |     |

| 6.1.4. Cache Clear Control                                                   |     |

| 6.1.4. Cache Clear Control 6.1.5. Memory-Mapped Registers 6.2. CMU Registers | 151 |

| 6.2.1. CMU register summary 1                                             | 52 |

|---------------------------------------------------------------------------|----|

| 6.2.2. CMU register descriptions                                          | 53 |

| 7. Advanced Core Local Interruptor (ACLINT)                               |    |

| 7.1. Features 1                                                           |    |

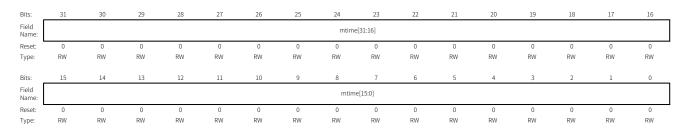

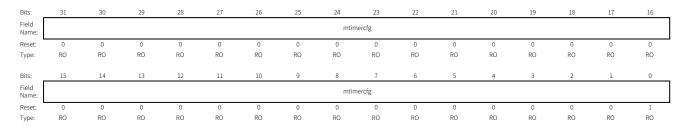

| 7.2. Registers                                                            | 64 |

| 7.2.1. Register Summary                                                   |    |

| 7.2.2. Register Description 10                                            |    |

| 7.3. Operations 10                                                        |    |

| 7.3.1. Timer Interrupt                                                    |    |

| 7.3.2. Software interrupt                                                 |    |

| B. Platform-Level Interrupt Controller (PLIC).                            |    |

| 8.1. Features 1                                                           |    |

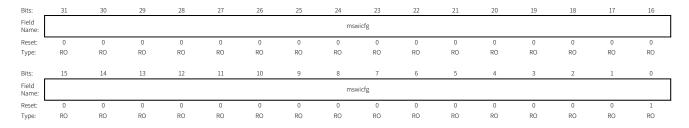

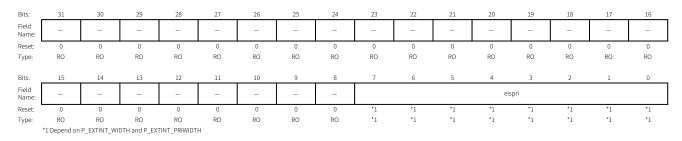

| 8.2. Registers                                                            |    |

| 8.2.1. Register Summary                                                   |    |

| 8.2.2. Register Description 1                                             |    |

| 8.3. Operations 1                                                         |    |

| 8.3.1. Software Settings                                                  |    |

| 8.3.2. Example of the Interrupt Processing Flow                           |    |

| a. S. S. Example of the interrupt Frocessing Flow  Debug Subsystem (DBG). |    |

|                                                                           |    |

| 9.1. Features 1  10. Functional Safety 1                                  |    |

| 10.1. Overview 1                                                          |    |

|                                                                           |    |

| 1.1.1. Catting of Book Initial Value Circula                              |    |

| 11.1. Setting of Reset Initial Value Signals                              |    |

| 11.2. DFT Signal Control                                                  |    |

| 12. NS31A Configuration Parameter and Port List 1                         |    |

| 12.1. Configuration Parameter List                                        |    |

| 12.2. Port List                                                           |    |

| 12.2.1. NS31A UIL Port List (AXI Configuration)                           |    |

| 12.2.2. NS31A CX Port List (AXI Configuration)                            |    |

| 12.2.3. NS31A DBG Port List (AXI Configuration)                           |    |

| 12.2.4. NS31A MEM Port List (AXI Configuration) 20                        |    |

| 12.2.5. NS31A UIL Port List (AHB Configuration)                           | 01 |

| 8 ,                                                                       | 03 |

| 12.2.7. NS31A DBG Port List (AHB Configuration)                           |    |

| 12.2.8. NS31A MEM Port List (AHB Configuration).                          |    |

| Appendix A: NS31A CSR Register                                            | 07 |

| Appendix B: NS31A Internal Register                                       |    |

| Appendix C: Instruction Table                                             | 19 |

| C.1. Legend 2                                                             | 19 |

| C.2. RV32I, Zicsr, Zifencei, SYSTEM                                       | 20 |

| C.3. RV32M                                                                | 22 |

| C.4. RV32A                                                                | 23 |

| C.5. RV32C                                                                | 24 |

| C.6. RV32F                                                                | 26 |

| C.6.1. RV32F instructions (scalar floating-point instructions)            | 26 |

| C.6.2. RV32F instructions (NS31A unique additional instructions)          |    |

| C.7. RV32B                                                                |    |

| Appendix D: Instruction OpCode Table                                      |    |

| D.1. RV32F                                                                |    |

| D.1.1. RV32F (NS31A custom)                                               | 30 |

| Revision History                                                          |    |

|                                                                           |    |

| Change History                                        | 232 |

|-------------------------------------------------------|-----|

| Differences between Revision 2.0.0 and Revision 3.0.0 | 232 |

| Additional Specifications                             | 232 |

| Specification Change                                  | 233 |

| Supplementary Explanation                             |     |

| Differences between Revision 1.0.1 and Revision 2.0.0 |     |

| Additional Specifications                             |     |

| Specification Change                                  | 244 |

| Supplementary Explanation                             |     |

| Differences between Revision 1.0.0 and Revision 1.0.1 | 245 |

| Additional Specifications                             | 245 |

| Specification Change                                  | 246 |

| Supplementary Explanation                             | 246 |

# **About This Document**

This document is a User Manual for NS31A.

It provides the hardware configuration and logic specifications for NS31A, as well as information on interfaces with external modules.

The target readers of the document are designers and software programmers who will implement systems with NS31A mounted.

For details of the specifications, see the NSITEXE NS31A Technical Reference Manual.

# **Notices and Disclaimers**

This document is Non-Confidential, but protected by copyright and other related rights.

The right to use, copy and disclose this document is subject to license restrictions in accordance with the terms of any relevant agreements. No license, express or implied, to any intellectual property rights is granted by this document.

This document is provided "AS IS". NSITEXE expressly disclaims all warranties, representations, and conditions of any kind, whether express or implied, including, but not limited to, the implied warranties or conditions of merchantability, fitness for a particular purpose and non-infringement.

NSITEXE does not assume any liability arising out of any use of this document, and specifically disclaims any and all liability, including without limitation indirect, incidental, special, exemplary, or consequential damages.

The party that NSITEXE provided this document shall be responsible for ensuring that any use of this document complies fully with any relevant export laws and regulations.

If any of the provisions contained in this document conflict with any terms of relevant agreements, the terms of agreements prevail over and supersede the conflicting provisions of this document. NSITEXE may make changes to this document at any time and without notice.

Product and company names that are referred to in this document may be trademarks or registered trademarks of their respective owners.

# **Target Design**

This document is intended for the following hardware design kit.

• NRV31210003

# **Relevant Documents**

- NSITEXE NS31A Technical Reference Manual (NRV31220000)

- NSITEXE NS31A Integration Manual (NRV31220002)

• NSITEXE NS31A Hardware Safety Manual (NRV31810001)

# **Reference Documents**

| Item# | Document                                                                                 | Revision Used              | Comment                       |

|-------|------------------------------------------------------------------------------------------|----------------------------|-------------------------------|

| 1     | The RISC-V Instruction Set Manual Volume I:<br>Unprivileged ISA                          | 20190608-Base-Ratified     |                               |

| 2     | The RISC-V Instruction Set Manual Volume II:<br>Privileged Architecture                  | 20211105-signoff           |                               |

| 3     | The RISC-V Instruction Set Manual Volume II:<br>Privileged Architecture                  | draft-20221004-28b46de     | Only for Smrnmi specification |

| 4     | RISC-V Debug Support                                                                     | 1.0.0-STABLE               |                               |

| 5     | RISC-V Bitmanip Extension                                                                | 1.0.0                      |                               |

| 6     | RISC-V Advanced Core Local Interruptor<br>Specification                                  | 1.0-rc4                    |                               |

| 7     | RISC-V Platform-Level Interrupt Controller<br>Specification                              | 1.0.0                      |                               |

| 8     | AMBA® AXI™ and ACE™ Protocol Specification<br>AXI3, AXI4, and AXI4-Lite ACE and ACE-Lite | ARM IHI 0022D (ID102711)   |                               |

| 9     | AMBA® APB Protocol Version: 2.0 Specification                                            | ARM IHI 0024C (ID041610)   |                               |

| 10    | AMBA® AHB Protocol Specification                                                         | ARM IHI 0033B.b (ID102715) |                               |

# **Abbreviations**

| Abbreviation | Description                         |

|--------------|-------------------------------------|

| ВТВ          | Branch Target Buffer                |

| CMU          | Core Management Unit                |

| CSR          | Control and Status Register         |

| DBG          | Debug Subsystem                     |

| DFT          | Design For Test                     |

| DLM          | Data Local Memory                   |

| ECC          | Error Correction Code               |

| EDC          | Error Detection and Correction      |

| hart         | Hardware Thread                     |

| ACLINT       | Advanced Core Local Interruptor     |

| PLIC         | Platform-Level Interrupt Controller |

| ILM          | Instruction Local Memory            |

| ISA          | Instruction Set Architecture        |

| PMP          | Physical Memory Protection          |

| TAP          | Test Access Port                    |

# Chapter 1. NSITEXE NS31A Core Overview

This chapter describes the overview of NSITEXE NS31A Processor.

NS31A is a 32-bit processor core optimized for control-specific microcontrollers.

The core supports the instruction sets of RISC-V, which is an open architecture. Therefore, this product can be used in various eco-systems.

The advanced, high-performance AXI configuration or the small-area AHB configuration can be selected using a configuration parameter.

# 1.1. Features

NS31A has the following features.

NS31A Core

- 32-bit processor core with a 4-stage pipeline structure and some RISC-V instruction sets

- Base Integer Instruction Set (RV32I or RV32E)

(When configuration parameter P\_RV32E is 1, RV32E is enabled.)

- Compressed Instructions (RV32C)

(Only when configuration parameter P\_RV32C is 1)

- Bit Manipulation Instructions (RV32B)

(Only when configuration parameter P\_RV32B is 1)

- Single-Precision Floating Point (RV32F)

(Only when configuration parameter P\_FPU is 1)

- Branch prediction mechanism with a Branch Target Buffer (BTB)

(Only when configuration parameter P\_BTB is 1)

- 2-stage privilege modes (M-mode and U-mode)

- 2 configuration options for the integer multiplier

(Can be changed using configuration parameter P\_MUL\_SMALL.)

- 2 configuration options for the integer divider

(Can be changed using configuration parameter P\_DIV\_SMALL.)

Instruction Cache (IC)

- 32-Byte Line 2-way Set Associative Cache

- Variable capacity

(Using configuration parameter P\_CACHE\_SIZE\_IC, the capacity can be selected from none to 32 KB.)

# Instruction Local Memory (ILM)

- Allocated only in the AXI configuration.

- Can be allocated in a given address space.

- Variable capacity

(Using configuration parameter P\_ADDR\_SIZE\_ILM, the capacity can be selected from none to 8 MB.)

#### Data Local Memory (DLM)

- Allocated only in the AXI configuration.

- Can be allocated in a given address space.

- Variable capacity

(Using configuration parameter P\_ADDR\_SIZE\_DLM, the capacity can be selected from 4 KB to 8 MB.)

# Interrupt Control Units (ACLINT/PLIC)

- External Interrupts with a priority processing mechanism that can support up to 255 factors

- Non-Maskable Interrupts that can be requested from the outside

- Software Interrupts which can directly be requested by accessing a register

- Timer interrupt from Internal Timer

# Core Management Unit (CMU)

• System control and observation functions using register interfaces

#### **Bus Interface**

- In the case of the AXI configuration

- System Bus Master interface (32-bit AXI4 Master) assuming access to resources in SoC

- External Peripheral Bus Master interface (32-bit APB4 Master) assuming access to registers of peripheral modules, etc.

- Front Port Bus Slave interface (32-bit AXI4 Slave) assuming access from an external master to internal RAM resources and registers

- In the case of the AHB configuration

- Instruction Memory Bus (32-bit AHB5 lite Master) for fetching instructions

- Data Memory Bus (32-bit AHB5 lite Master) for access data in memory and registers in SoC

- $\circ~$  Peripheral Bus Slave (32-bit APB4 Slave) for access to registers in NS31A

# **Functional Safety**

- Physical Memory Protection for protecting address spaces (The number of entries can be changed using configuration parameter P\_PMPNUM.)

- RAM ECC for protecting RAM data (When configuration parameter P\_REDUNDANT is 1 or 2)

- Bus Error Detection and Correction (EDC) for protecting buses (Only when configuration parameter P\_REDUNDANT is 2 in the AXI configuration)

- Dual Core Lock-Step for realizing redundancy (only when configuration parameter P\_REDUNDANT is 2)

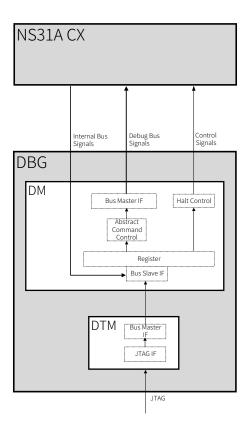

# Debug Unit

- Controls the execution of the hart

- Debug resource access by a JTAG debugger or via a bus

- Compliant with RISC-V External Debug Specification

# 1.2. Function Block Diagram

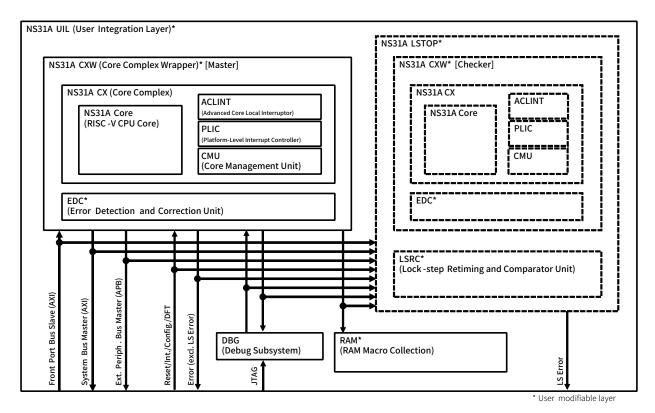

Figure 1 shows the block diagram of the AXI configuration of the NSITEXE NS31A processor.

Figure 1. NS31A Block Diagram (AXI configuration)

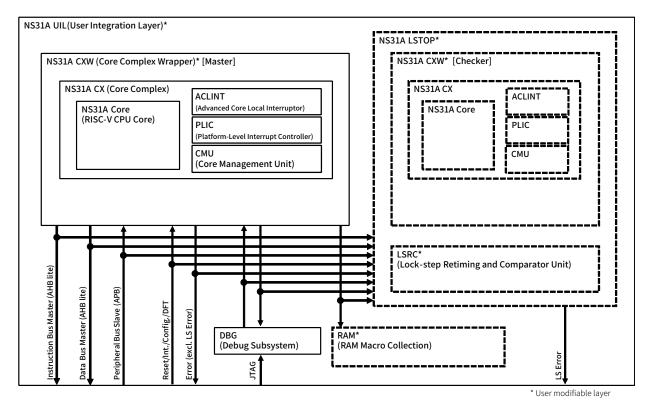

Figure 2 shows the block diagram of the AHB configuration of the NSITEXE NS31A processor.

Figure 2. NS31A Block Diagram (AHB configuration)

The following layers are implementation samples, which can be modified by the user.

NS31A User Integration Layer (UIL) Top layer of NS31A for use by the user. NS31A Lock-Step Top (LSTOP) Layer to be added when NS31A is used in the Dual Core Lock-Step. Implemented only when configuration parameter P\_REDUNDANT is 2. NS31A Core Complex Wrapper (CXW) Wrapper layer for integrating NS31A CX and NS31A EDC. Error Detection and Correction Unit (EDC) Unit for performing bus, RAM ECC, and parity processing. It consists of RAM ECC and BUS EDC. RAM ECC is implemented when configuration parameter P\_REDUNDANT is 1 or 2. BUS EDC is implemented only when configuration parameter P\_REDUNDANT is 2 in the AXI configuration. BUS EDC is not implemented in the AHB configuration. Lock-Step Retiming and Comparator Unit (LSRC) Unit for allocating a retiming (delay) FF and a comparator for a Lock-Step configuration. Implemented only when configuration parameter P\_REDUNDANT is 2.

RAM Macro module. This layer and the layers below it need

to be implemented by the user according to the process to

be used.

The following layers and the layers below them cannot be modified by the user.

NS31A Core Complex (CX)

Layer on which the NS31A Core and peripheral units are

integrated.

NS31A Core RISC-V CPU Core of NS31A.

Advanced Core Local Interruptor (ACLINT) Unit for controlling the core local interrupts.

**Platform-Level Interrupt Controller (PLIC)** Unit for controlling the external interrupts.

**Core Management Unit (CMU)**Unit for controlling and monitoring the operations in the core.

**Debug Subsystem (DBG)**Unit in which debug mechanisms are integrated.

# Chapter 2. Memory Map

This chapter describes the memory map of NS31A and the behavior of each memory access operation.

# 2.1. Address Map

# 2.1.1. Address Regions

The memory and register resources in NS31A are allocated in the address regions shown in Table 1, respectively.

In the AXI configuration, regions other than these are External System Bus regions. Access from NS31A to any of these regions causes access from the System Bus Master. The resources in the address regions shown in Table 1 can be accessed from an external bus master via the Front Port Bus Slave.

In the AHB configuration, Instruction Local Memory and Data Local Memory are not mounted in NS31A. Also, the External Peripheral Bus is not implemented. NS31A makes instruction access to all addresses from the Instruction Bus Master and data access from the Data Bus Master. Only register regions can be accessed from an external bus master only via the Peripheral Bus Slave.

Access may result in an error response.

In the AXI configuration, error responses are classified into SLVERR and DECERR. The response classifications are indicated in the following descriptions.

In the AHB configuration, error responses are not classified.

SLVERR and DECERR errors in the AXI configuration and bus errors in the AHB configuration are not classified by software. An error caused by a Load instruction is notified as a non-blocking load bus error NMI, and an error caused by a Store or AMO instruction is notified as a non-blocking store bus error NMI. For details, see Section 3.12.3.

In NS31A, IP is designed with incorporation into a SoC system in mind. Therefore, there is no specific absolute address on the address map of each resource.

The start address of each region and the size of some address regions will be given by specifying them in relevant parameters when IP is implemented. The start address specified in the parameter needs to be aligned with the address region size.

For details, see Section 12.1.

Table 1. Address Region List

| Region                   | Start Address (Parameter) | Size (Parameter)     | Description              |

|--------------------------|---------------------------|----------------------|--------------------------|

| Instruction Local Memory | P_ADDR_BASE_ILM (*1)      | P_ADDR_SIZE_ILM (*1) | The size can be changed. |

| Data Local Memory        | P_ADDR_BASE_DLM (*1)      | P_ADDR_SIZE_DLM (*1) | The size can be changed. |

| External Peripheral Bus  | P_ADDR_BASE_PER (*1)      | P_ADDR_SIZE_PER (*1) | The size can be changed. |

| Debug Subsystem Register | P_ADDR_BASE_DBG           | Fixed to 16 KB.      |                          |

| Hart Context Register    | P_ADDR_BASE_HCR           | Fixed to 32 KB.      |                          |

| ACLINT Register          | P_ADDR_BASE_ACLINT        | Fixed to 64 KB.      |                          |

| Region            | Start Address (Parameter) | Size (Parameter) | Description |

|-------------------|---------------------------|------------------|-------------|

| CMU Register      | P_ADDR_BASE_CMU           | Fixed to 4 KB.   |             |

| Internal Register | P_ADDR_BASE_REG           | Fixed to 4 KB.   |             |

| PLIC Register     | P_ADDR_BASE_PLIC          | Fixed to 4 MB.   |             |

<sup>\*1</sup> In the AHB configuration, these configuration parameters are disabled.

# 2.1.1.1. Instruction Local Memory Region Address Map

Table 2 shows the address map of the Instruction Local Memory (ILM) Region.

The external bus master of NS31A can also access this region via the Front Port Bus Slave interface.

Table 2. ILM Region Address Map (P\_ADDR\_BASE\_ILM + Offset)

| Start Address | End Address              | Region | Size                  |

|---------------|--------------------------|--------|-----------------------|

| +0x00_0000    | +size(P_ADDR_SIZE_ILM)-1 | ILM    | size(P_ADDR_SIZE_ILM) |

This region is not implemented if the AHB configuration is selected (configuration parameter P\_ADDR\_SIZE\_ILM is disabled).

Even when the AXI configuration is selected, the region is not implemented if NS31A is configured with configuration parameter P\_ADDR\_SIZE\_ILM set to 0.

### 2.1.1.2. Data Local Memory Region Address Map

Table 3 shows the address map of the Data Local Memory (DLM) Region.

The external bus master of NS31A can also access this region via the Front Port Bus Slave interface.

Table 3. DLM Region Address Map (P\_ADDR\_BASE\_DLM + Offset)

| Start Address | End Address              | Region | Size                  |

|---------------|--------------------------|--------|-----------------------|

| +0x00_0000    | +size(P_ADDR_SIZE_DLM)-1 | DLM    | size(P_ADDR_SIZE_DLM) |

This region is not implemented if the AHB configuration is selected (configuration parameter P\_ADDR\_SIZE\_DLM is disabled).

### 2.1.1.3. External Peripheral Bus Region Address Map

Table 4 shows the address map of the External Peripheral Bus Region.

Access to this region is access to the External Peripheral Bus. For details of the External Peripheral Bus Master, see Section 4.1.2.

The external bus master of NS31A can also access this region via the Front Port Bus Slave interface.

Do not allocate an instruction code in this region.

Table 4. External Peripheral Bus Region Address Map (P\_ADDR\_BASE\_PER + Offset)

| Start Address | End Address              | Region                  | Size                  |

|---------------|--------------------------|-------------------------|-----------------------|

| +0x00_0000    | +size(P_ADDR_SIZE_PER)-1 | External Peripheral Bus | size(P_ADDR_SIZE_PER) |

This region is not implemented if the AHB configuration is selected (configuration parameter P\_ADDR\_SIZE\_PER is

disabled). Even when the AXI configuration is selected, the region is not implemented if NS31A is configured with configuration parameter P\_ADDR\_SIZE\_PER set to 0.

#### 2.1.1.4. Internal Register Region Address Map

Table 5 shows the address map of the Internal Register Region.

This is a region where internal control registers are allocated. The external bus master of NS31A can also access this region via the Front Port Bus Slave in the case of the AXI configuration or via the Peripheral Bus Slave interface in the case of AHB configuration.

Table 5. Internal Register Region Address Map (P\_ADDR\_BASE\_REG + Offset)

| Start Address | End Address | Region                         | Size |

|---------------|-------------|--------------------------------|------|

| +0x0000       | +0x0FFF     | Memory Mapped Control Register | 4KB  |

When a reserved region in the Region in Table 5 is accessed, a bus error response is returned (DECERR in the case of the AXI configuration).

If P\_BUS\_PROT0\_PRIV parameter is set to 1, the following error responses are returned.

- If the Region is accessed from NS31A CORE with the U-mode privilege, a bus error response is returned.

- In the AXI configuration, if the Region is accessed from the Front Port Bus Slave with the AxPROT[0] = 0 (Unprivileged) privilege, a bus error response (SLVERR) is returned.

- In the AHB configuration, if the Region is accessed from the Peripheral Bus Slave with the PPROT[0] = 0 (Normal) privilege, an error response is returned.

#### 2.1.1.5. CMU Register Region Address Map

Table 6 shows the address map of the CMU Register Region.

This is a region where internal control registers are allocated.

The external bus master of NS31A can also access this region via the Front Port Bus Slave in the case of the AXI configuration or via the Peripheral Bus Slave interface in the case of AHB configuration.

Table 6. CMU Register Region Address Map (P\_ADDR\_BASE\_CMU + Offset)

| Start Address | End Address | Region               | Size |

|---------------|-------------|----------------------|------|

| +0x0000       | +0x0FFF     | CMU control register | 4KB  |

When a reserved region in the Region in Table 6 is accessed, 0 is read for a read access and a write access is ignored. If P\_BUS\_PROT0\_PRIV parameter is set to 1, the following error responses are returned.

- If the Region is accessed from NS31A CORE with the U-mode privilege, a bus error response is returned.

- In the AXI configuration, if the Region is accessed from the Front Port Bus Slave with the AxPROT[0] = 0 (Unprivileged) privilege, a bus error response (SLVERR) is returned.

- In the AHB configuration, if the Region is accessed from the Peripheral Bus Slave with the PPROT[0] = 0 (Normal) privilege, an error response is returned.

#### 2.1.1.6. ACLINT Register Region Address Map

Table 7 shows the address map of the ACLINT Register Region.

This is a region where internal control registers are allocated. The external bus master of NS31A can also access this region via the Front Port Bus Slave in the case of the AXI configuration or via the Peripheral Bus Slave interface in the case of AHB configuration.

Table 7. ACLINT Register Region Address Map (P\_ADDR\_BASE\_ACLINT + Offset)

| Start Address | End Address | Region                  | Size |

|---------------|-------------|-------------------------|------|

| +0x0000       | +0xFFFF     | ACLINT control register | 64KB |

When an unused region in the Region in Table 7 is accessed, 0 is read for a read access and a write access is ignored. If P\_BUS\_PROT0\_PRIV parameter is set to 1, the following error responses are returned.

- If the Region is accessed from NS31A CORE with the U-mode privilege, a bus error response is returned.

- In the AXI configuration, if the Region is accessed from the Front Port Bus Slave with the AxPROT[0] = 0 (Unprivileged) privilege, a bus error response (SLVERR) is returned.

- In the AHB configuration, if the Region is accessed from the Peripheral Bus Slave with the PPROT[0] = 0 (Normal) privilege, an error response is returned.

### 2.1.1.7. PLIC Register Region Address Map

Table 8 shows the address map of the PLIC Register Region.

This is a region where internal control registers are allocated. The external bus master of NS31A can also access this region via the Front Port Bus Slave in the case of the AXI configuration or via the Peripheral Bus Slave interface in the case of AHB configuration.

Table 8. PLIC Register Region Address Map (P\_ADDR\_BASE\_PLIC + Offset)

| Start Address | End Address | Region                | Size |

|---------------|-------------|-----------------------|------|

| +0x000000     | +0x3FFFFF   | PLIC control register | 4MB  |

When an unused region in the Region in Table 8 is accessed, 0 is read for a read access and a write access is ignored. If P\_BUS\_PROT0\_PRIV parameter is set to 1, the following error responses are returned.

- If the Region is accessed from NS31A CORE with the U-mode privilege, a bus error response is returned.

- In the AXI configuration, if the Region is accessed from the Front Port Bus Slave with the AxPROT[0] = 0 (Unprivileged) privilege, a bus error response (SLVERR) is returned.

- In the AHB configuration, if the Region is accessed from the Peripheral Bus Slave with the PPROT[0] = 0 (Normal) privilege, an error response is returned.

# 2.1.1.8. Hart Context Register Region Address Map

Table 9 shows the address map of the Hart Context Register Region.

This is a region where internal control registers are allocated. The external bus master of NS31A can also access this region via the Front Port Bus Slave in the case of the AXI configuration or via the Peripheral Bus Slave interface in the

case of AHB configuration.

Table 9. Hart Context Register Region Address Map (P\_ADDR\_BASE\_HCR + Offset)

| Start Address | End Address | Region                | Size |

|---------------|-------------|-----------------------|------|

| +0x0000       | +0x7FFF     | Hart context register | 32KB |

The following access to this region causes a bus error response (SLVERR in the case of the AXI configuration).

Access to an unused area in this region

In the case of the AXI configuration, the following access to this region causes a bus error response (SLVERR).

- Access from NS31A CORE with the U-mode privilege (only in case of P\_BUS\_PROT0\_PRIV=1)

- Instruction fetch access from NS31A CORE

- Access from the Front Port Bus Slave with AxPROT[0] set to 0 (Unprivileged) (only in case of P\_BUS\_PROT0\_PRIV=1)

- Access from the Front Port Bus Slave with AxPROT[2] set to 1 (Instruction)

In the case of the AHB configuration, the following access to this region causes a bus error response.

- Access from the Peripheral Bus Slave with the PPROT[0] = 0 (Normal) privilege (only in case of P\_BUS\_PROT0\_PRIV=1)

- Access from the Peripheral Bus Slave with the PPROT[2] = 1 (Instruction) privilege

There are also other conditions that cause a bus error response. For details, see Section 3.8.2.

# 2.1.1.9. Debug Subsystem Register Region Address Map

Table 10 shows the address map of the Debug Subsystem Register Region.

This region can be accessed from the external bus master of NS31A via the Front Port Bus Slave in the case of the AXI configuration or via the Peripheral Bus Slave interface in the case of AHB configuration.

Table 10. Debug Subsystem Register Region Address Map (P\_ADDR\_BASE\_DBG + Offset)

| Start Address | End Address | Region                | Size |

|---------------|-------------|-----------------------|------|

| +0x0000       | +0x00FF     | Safe Zero Address     | 256B |

| +0x0100       | +0x03FF     | Reserved              | 768B |

| +0x0400       | +0x05FF     | Debug module register | 1KB  |

| +0x0600       | +0x2FFF     | Reserved              | 10KB |

| +0x3000       | +0x3FFF     | Error Device          | 4KB  |

#### Access to Safe Zero Address region

If the Safe Zero Address region in this region is accessed from NS31A CORE, Front Port Bus Slave, or Peripheral Bus Slave, A write access is ignored and a read data is always zero. No bus error response occurs.

#### Access to Reserved region

If the Reserved region in this region is accessed from NS31A CORE, Front Port Bus Slave, or Peripheral Bus Slave, a bus error response is returned (SLVERR in the case of the AXI configuration).

#### Access to Error Device region

If the Error Device region in this region is accessed from NS31A CORE, Front Port Bus Slave, or Peripheral Bus Slave, a bus error response is returned (SLVERR in the case of the AXI configuration).

### Access to Debug module register

If an unused region in the Debug module register is read, an undefined value is returned. A write access is ignored. In such cases, bus access is completed normally and functions other than bus access are not affected.

Accessing the Debug module register is restricted by the Debug Authentication function.

If the input value of the dbg\_auth signal is 0, any access to this region causes a bus error response (DECERR in the case of the AXI configuration).

For details of the Debug Authentication function, see NSITEXE NS31A Technical Reference Manual.

# Access with the U-mode privilege

When P\_BUS\_PROT0\_PRIV parameter is set to 1, the following bus errors are returned.

- In the case of the AXI configuration, if this region is accessed from NS31A Core with the U-mode privilege, a bus error response (DECERR) is returned.

- If access is made from the Front Port Bus Slave with the AxPROT[0] = 0 (Unprivileged) privilege, a bus error response (SLVERR) is returned.

- In the case of the AHB configuration, if access is made from the Peripheral Bus Slave with the PPROT[0] = 0 (Normal) privilege, a bus error response is returned.

# 2.1.2. Bus access routing

In NS31A, the region that can be accessed differs depending on the master.

Table 11 shows the region that can be accessed from each master in the case of the AXI configuration. If an inaccessible region is accessed, a bus error response (DECERR) is returned.

Table 11. Space That Can Be Accessed from Each Master(AXI configuration)

| Region                   | CPU      | Front Port Bus Slave |

|--------------------------|----------|----------------------|

| Instruction Local Memory | <b>~</b> | <b>~</b>             |

| Data Local Memory        | ✓        | <b>~</b>             |

| External Peripheral Bus  | ~        | <b>~</b>             |

| Debug Subsystem Register | ~        | <b>~</b>             |

| Hart Context Register    | ~        | <b>~</b>             |

| ACLINT Register          | ~        | <b>~</b>             |

| CMU Register             | ~        | <b>~</b>             |

| Internal Register        | ~        | <b>~</b>             |

| PLIC Register            | ~        | <b>~</b>             |

| External System Bus      | ~        | -                    |

In the AHB configuration, all address regions can be accessed as a flat address space.

Instruction access is issued from the Instruction Bus Master Interface, and data access is issued from the Data Bus Master Interface.

Instruction Local Memory, Data Local Memory, and External Peripheral Bus are not implemented.

The regions of ACLINT Register, CMU Register, PLIC Register, Internal Register, Hart Context Register, and Debug Subsystem Register can be accessed as part of address spaces from the Peripheral Bus Slave via the external bus. Note, however, that instructions cannot be allocated in the address regions of ACLINT Register, CMU Register, PLIC Register, Internal Register, and Hart Context Register.

If an inaccessible region is accessed, a bus error response is returned.

Bus access from DBG is prohibited. During debugging, use Abstract Command to access from the CPU. For details, see NSITEXE NS31A Technical Reference Manual.

### 2.1.2.1. Address Region Attribute

Each address region has the following attributes defined independently.

#### Cacheable

This indicates whether the instruction cache is enabled or disabled in the address region. However, whether data is actually cached or not differs depending on individual factors (e.g. in the Debug Mode, when the cache is disabled, etc.).

#### Side effect

This indicates whether the read/write operation from/to an address region has a side effect. If there is no side effect, idempotence is guaranteed for the region (generally, I/O registers and control registers have a side effect). It is impossible to combine a write operation to a region where idempotence is not guaranteed.

Table 12 shows whether each address region has these attributes in the case of the AXI configuration. In the case of the AHB configuration, all address regions are "cacheable" and "have a side effect".

Table 12. Whether Each Address Region Has These Attributes (AXI Configuration)

| Region                   | Cacheable | Side effect |

|--------------------------|-----------|-------------|

| Instruction Local Memory | Yes       | No          |

| Data Local Memory        | Yes       | No          |

| External Peripheral Bus  | Yes       | Yes         |

| Debug Subsystem Register | Yes       | Yes         |

| Hart Context Register    | *1        | Yes         |

| ACLINT Register          | *1        | Yes         |

| CMU Register             | *1        | Yes         |

| Internal Register        | *1        | Yes         |

| PLIC Register            | *1        | Yes         |

| External System Bus      | Yes       | Yes         |

<sup>\*1</sup> This is a cacheable region, but no instruction codes can be allocated to it.

For the support status of mutual exclusion instructions (RV32A) in each address region, see Section 3.10.

Access to an address region with a side effect is controlled so that an access request will not be split nor combined.

# 2.2. RAM

This chapter describes the RAM mounted in NS31A.

Table 13 shows the list of RAMs in NS31A.

ILM and DLM are not mounted in the AHB configuration. IC is not mounted when configuration parameter P\_CACHE\_SIZE\_IC is 0, and ILM is not mounted when configuration parameter P\_ADDR\_SIZE\_ILM is 0. The functions related to unmounted RAMs that are described below are disabled.

Table 13. RAM List

| RAM                            | NS31A   |

|--------------------------------|---------|

| Instruction Cache (IC)         | 0B~32KB |

| Instruction Local Memory (ILM) | 0B~8MB  |

| Data Local Memory (DLM)        | 4KB~8MB |

## 2.2.1. Features

#### Access

The bus masters in NS31A and the masters connected to the Front Port can access all RAMs (ILM and DLM) that have addresses.

The address allocation is determined by the parameters shown in Section 2.1.1.

#### Test interface

All the RAMs including caches have a test interface that can be accessed from the software.

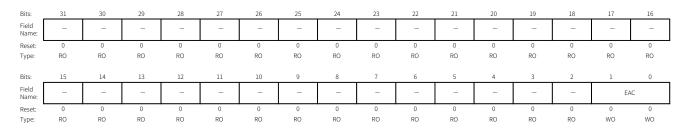

### 2.2.1.1. Test interface

Table 14 shows the test interface of each RAM in NS31A.

# direct memory access

Implies the test that is conducted via a normal memory access route.

#### in-direct memory access via control register

Implies the access that is performed via a control register.

Table 14. RAM Test interface

| RAM              | Address mapping | Test interface for Data RAM                  |

|------------------|-----------------|----------------------------------------------|

| ILM              | mapped          | direct memory access                         |

| DLM              | mapped          | direct memory access                         |

| Inst. Cache Tag  | unmapped        | in-direct memory access via control register |

| Inst. Cache Data | unmapped        | in-direct memory access via control register |

For details of the control registers that access the internal RAM in the Instruction Cache, see Section 3.8.3. To access the internal RAM of a cache, see Section 2.3.3.4.

# 2.3. Cache Control

This chapter describes the cache system of NS31A. NS31A has the following cache.

Level-1: Instruction Cache

(Only when configuration parameter P\_CACHE\_SIZE\_IC ≥ 1)

The Level-1 Instruction Cache caches the instruction fetch target address and neighboring area. Note that it does not cache literals.

In NS31A, the Level-1 Instruction Cache is enabled for all the address regions when P\_CACHE\_SIZE\_IC  $\geq 1$ . However, when the hart state is the Debug mode, it is always disabled, regardless of the address or cache setting.

#### 2.3.1. Features

Each cache has the following control functions.

These functions are controlled via control registers or Cache Clear signals, which are external pin inputs.

- Enabling/disabling caches

- Cache flush

- Register setting

- · External pin input

- Diagnosis access

These functions are not available when configured with P\_CACHE\_SIZE\_IC set to 0.

# 2.3.2. Registers

#### 2.3.2.1. Instruction Cache registers

The cache control registers of the Instruction Cache and the control registers that controls access to the internal RAM of the cache are provided as the memory mapped registers of the processor. See Section 3.8.3.

# 2.3.3. Operations

#### 2.3.3.1. Cache enable/disable

To control whether to enable or disable a cache, perform the following procedure.

- Enabling a cache

- 1. Write 1 to bit 0 (Cache Enable) of the ml1cachesysctrl register.

- 2. Execute the FENCE instruction.

- 3. When a write complete response is returned, the enabling is completed.

- Disabling a cache

- 1. Write 0 to bit 0 (Cache Enable) of the ml1cachesysctrl register.

- 2. Execute the FENCE instruction.

- 3. When a write complete response is returned, the disabling is completed.

#### 2.3.3.2. Cache clear (register setting)

To control the clearing of a cache by using a register, perform one of the following procedures.

- Clear control via register access

- 1. Write 1 to bit 0 (Flush Operation) of the ml1cacheoperation register.

- If the mllcacheoperation register is accessed using the store instruction when P\_CACHE\_SIZE\_IC is set to 0, a bus error occurs.

The value of P\_CACHE\_SIZE\_IC can be checked using the CFGCSIZEIC register of the CMU.

Make this check as necessary before accessing mllcacheoperation.

- When writing data to the mllcacheoperation register using the store instruction, execute the FENCE instruction to wait for the completion of clearing the cache.

- Clear control using the CMU register access

- 1. Read the CFGCSIZEIC register, and check the value of configuration parameter P\_CACHE\_SIZE\_IC.

- 2. When configuration parameter P\_CACHE\_SIZE\_IC  $\geq$  1, exercise clear control by taking steps 3 to 5 below.

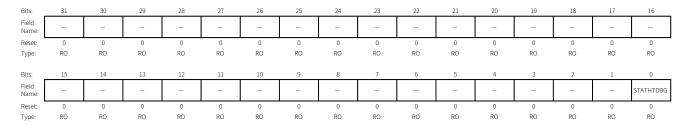

- 3. Write 1 to bit 16 (COMPCCLR) of the STATCCLR register to clear the completion flag to 0.

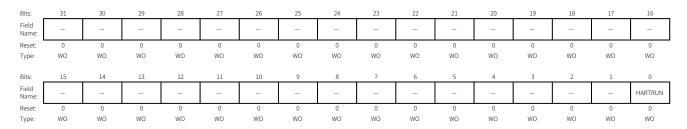

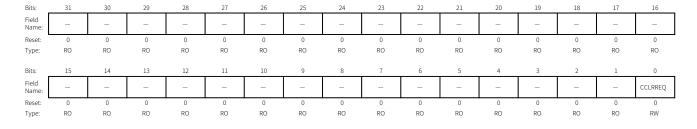

- 4. Write 1 to bit 0 (CCLRREQ) of the CTRLCCLR register.

- 5. When bit 16 (COMPCCLR) of the STATCCLR register becomes 1, the cache has been completely cleared.

## 2.3.3.3. Cache clear (external input pin)

The caches of NS31A can be cleared by asserting the external pin bccx\_cache\_clr\_req.

In this cache clearing, the completion of clearing the cache is notified to the outside by asserting ncc\_cache\_clr\_ack. Do not negate the asserted ncc\_cache\_clr\_req until ncc\_cache\_clr\_ack is asserted.

When executing the cache clearing again, have 5 or more cycles of the clk clock after the negation of ncc\_cache\_clr\_ack before asserting ncc\_cache\_clr\_req.

Under ideal conditions, the cache clearing is completed within 20 cycles after the request signal is asserted. The number of cycles until the cache is actually cleared is determined according to the internal state of NS31A. It is possible to check whether the cache has been completely cleared by checking the assertion of ncc\_cache\_clr\_ack or using the STATCCLR.COMPCCLR flag.

This function is disabled when no cache is mounted in the configuration.

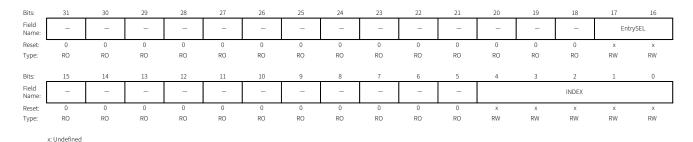

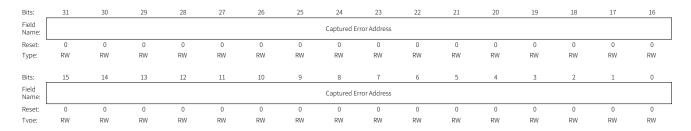

# 2.3.3.4. Diagnosis access

The caches of NS31A can be accessed by the registers for testing. To access the internal RAM of a cache, perform the following procedure.

(Only when configuration parameter  $P_CACHE_SIZE_IC \ge 1$ )

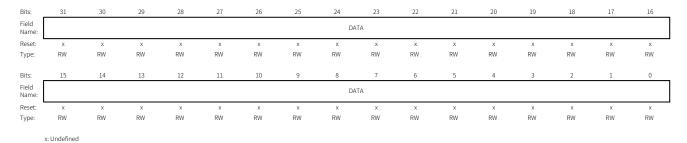

#### Procedure for write-access to the internal RAM of a cache

- 1. Set the access target RAM and address in the L1CRATGT register.

- 2. Set the lower 32 bits of Write Data in the L1CRADAT0 register.

- 3. To access DataRAM, set the upper 32 bits of Write Data in the L1CRADAT1 register.

- 4. Write 2 or 3 to the RAC[1:0] bits of the L1CRACTR register.

#### Procedure for read-access to the internal RAM of a cache

- 1. Set the access target RAM and address in the L1CRATGT register.

- 2. Write 1 to the RAC[1:0] bits of the L1CRACTRL register.

- 3. Read the lower 32 bits of Read Data from the L1CRADAT0 register.

- 4. To access DataRAM, read the upper 32 bits of Read Data from the L1CRADAT1 register.

# Chapter 3. NS31A Core

This chapter describes the NS31A Core that performs a series of arithmetic processing in NS31A.

# 3.1. Overview

The NS31A Core is a processor core designed in accordance with the RISC-V Instruction Set Architecture (ISA) standard. In the AXI configuration, it contains unique memories (ILM and DLM) that share address spaces and NS31A fetches instruction codes from these memories or from outside the core.

ILM and DLM are not mounted in the AHB configuration. Instruction codes are fetched from outside the core.

#### 3.1.1. Execution Control Part

The NS31A Core adopts a 4-stage pipeline structure with a branch prediction mechanism<sup>\*1</sup> that uses a Branch Target Buffer (BTB).

The Execution Control Part performs instruction execution, exception handling, interrupt processing, and error handling, among others.

\*1 The branch prediction mechanism is enabled only when configuration parameter P\_BTB is 1.

The instruction sets of NS31A are based on the RISC-V architecture.

For the instruction sets, see Section 3.9.

#### 3.1.2. Hardware Thread

The hardware thread (hart) in NS31A is equivalent to the hart defined in the RISC-V and equipped with thread contexts (PC, general-purpose register, and CSR).

For details of each CSR, see Section 3.7.

NS31A is equipped with one hart.

# 3.2. Physical Memory Protection (PMP)

This section describes memory protection using physical memory protection (PMP).

#### 3.2.1. Features

PMP is a mechanism that monitors an access address from the bus master to each memory region and detects illegal access to an address out of the specified range.

NS31A has the PMP implemented to protect the NS31A Core from instruction or data access.

The PMP is implemented only when configuration parameter  $P_PMPNUM \ge 1$ .

The PMP function is not available when configured with P\_PMPNUM set to 0. Access is always permitted.

PMP has the following functions.

#### Address check

- Address width: 32 bits

- Minimum region granularity

- Data: 4 bytes (32 bits)

- Instruction: 32 bytes (256 bits)

(For details of the minimum region granularity for instruction fetch, see Section 3.12.6.)

- Number of entries to be checked: Max. 16 (The number of entries can be changed using configuration parameter P\_PMPNUM.)

- Support the following address range settings specified in RISC-V Priv. Arch. V1.11 specifications.

- TOR: Top of range

Entry 0: 0x0 ≤ (target addr) < PMPADDR0</li>

Entry n: PMPADDRm ≤ (target addr) < PMPADDRn, (n=1-15, m=n-1)</li>

- NA4: Naturally aligned four-byte region

- ∘ NAPOT: Naturally aligned power-of-two region 2^n byte region (3  $\leq$  n  $\leq$  32), which is set in PMPADDR

## **Entry lock**

- Each PMP entry has a Lock bit (pmpncfg.L). Locking an entry protects it from being changed.

- Check the R/W/X permissions even in M-mode when locking an entry.

# Entry match, priority

- If the access address is within the address range of the entry, determine whether the access is permitted or not for the entry.

- If there are multiple entries that match an address (Overlapping), an entry with the smallest entry number has priority.

- In U-mode, always determine whether access is permitted for the entry. If there are no matching entries, access is illegal.

- In M-mode, determine whether the following accesses are permitted.

- Instruction fetch

- Determine whether access is permitted using only the PMP entries for which pmpncfg.L is set to 1.

- Access is permitted if there are no valid entries whose address matches.

- Data access

- When mstatus.MPRV = 1 and mstatus.MPP = 0 (access with U-mode privilege)

- Determine whether access is permitted using all PMP entries.

- Access is not permitted if there are no valid entries whose address matches.

- Other than the above

- Determine whether access is permitted using only the PMP entries for which pmpncfg.L is set to 1.

- Access is permitted if there are no valid entries whose address matches.

# Behavior performed if an illegal access occurs

- An exception occurs

- Error notification

In NS31A, an exception is generated if an illegal access occurs. For details of the an exception that is generated, see Section 3.4. An error notification is issued by asserting the err\_pmp signal for one cycle.

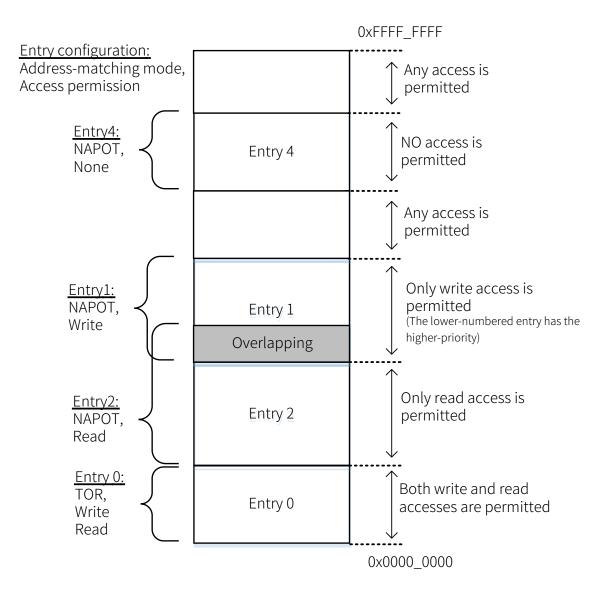

#### 3.2.1.1. Entry match and priority

An example of entry match and priority is shown in Figure 3.

Figure 3 shows a case where there is overlapping in entry settings. An entry with a smaller entry number has higher priority.

This example assumes that access is permitted in the register setting if no PMP entries match.

Figure 3. Example of overlapping PMP entries

# 3.2.1.2. Behavior in the Debug mode

While the hart is in the Debug mode, PMP does not perform access protection, regardless of the register settings.

# 3.2.2. Registers

For the PMP registers, see Section 3.7.2.7.

# 3.3. Operating States

NS31A has the following three types of states as a state indicating the operating state of each layer.

- System-level states

- Core-level states

- · Hart-level states

Table 15 shows the correspondence between layers and states.

Table 15. Operating States Level

| State               | Layer      |

|---------------------|------------|

| System-level states | NS31A      |

| Core-level states   | NS31A Core |

| Hart-level states   | hart0      |

The following shows the meaning of each state.

#### System-level states

System-level states are the states that NS31A has, which indicate the operating states of the core (and hart) and peripheral modules.

#### Core-level states

Core-level states are the states that the core (NS31A Core) has, which indicate the operating states of the core.

# Hart-level states

Hart-level states are the states that the hardware thread (hart) has, which indicate the operating states of the hart.

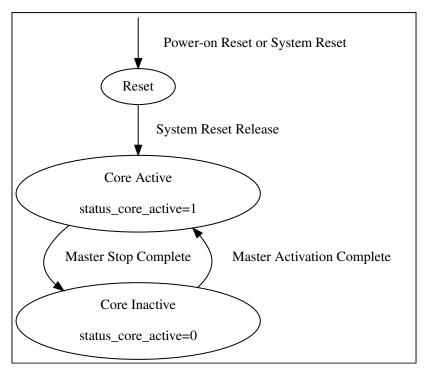

# 3.3.1. System-level states

System-level states are the states that NS31A (NS31A CX) has, which indicate the operating states of NS31A Core Complex.

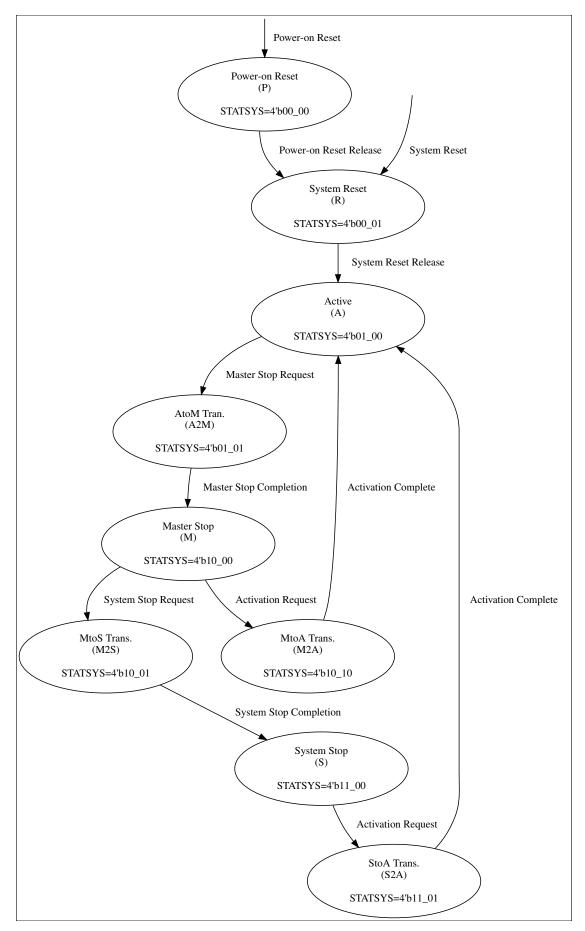

System-level states are controlled via the System Control pins on the NS31A CX layer. Be sure to assert the System Control pins only in a state that is indicated as a transition condition in Figure 4. For details of the control pins, see Table 161.

The operating states of NS31A CX are output to the NS31A CX output pin ncc\_stat.

The following explains each state and shows a state transition diagram.

For details of the System-level State transition timing, see Section 5.3.

Figure 4. System-level states Transition diagram

#### Power-on Reset

The state of power-ON reset. No functions of NS31A can be used.

# **System Reset**

The state of system reset. Except some system management functions, error functions, and debug-related functions, functions cannot be used.

#### Active

Active state. All functions of NS31A can be used.

#### **Master Stop**

Master stop state. The execution of programs is suspended, and the issuance of all bus transactions is stopped. It is possible to access registers and RAM in NS31A from the outside of NS31A via the Front Port Bus Slave (AXI configuration) or Peripheral Bus Slave (AHB configuration).

#### **System Stop**

System stop state. In addition to the stop of the Master Stop state, it is impossible to access the Front Port Bus Slave (AXI configuration) or Peripheral Bus Slave (AHB configuration) and an access request to a register or RAM cannot be accepted according to the bus protocol.

In this state, it is guaranteed that there are no unprocessed bus transactions in NS31A. Therefore, it is possible to execute the system reset of NS31A alone without affecting the external bus.

#### **AtoM Transition**

A state where the transition from Active to Master Stop is in progress.

#### **MtoS Transition**

A state where the transition from Master Stop to System Stop is in progress.

#### **MtoA Transition**

A state where the transition from Master Stop to Active is in progress.

#### **StoA Transition**

A state where the transition from System Stop to Active is in progress.

The following shows conditions for each state transition.

#### **Power-on Reset**

Perform the Power-on Reset according to the procedure described in Section 5.2.1.

# **System Reset**

Perform the System Reset according to the procedure described in Section 5.2.2.

#### Power-on Reset Release

Release the Power-on Reset according to the procedure described in Section 5.2.1.

# **System Reset Release**

Release the System Reset according to the procedure described in Section 5.2.2.

#### **Master Stop Request**

Assert ncc\_mststop\_req to request all bus masters to stop.

#### **Master Stop Completion**

The transition to this state is made when all bus masters have stopped.

At this time, assert ncc\_mststop\_ack to notify the outside about the completion.

# **System Stop Request**

Assert ncc\_sysstop\_req to request the system to stop.

### **System Stop Completion**

The transition to this state is made when the system has stopped. At this time, assert ncc\_sysstop\_ack to notify the outside about the completion.

#### **Activation Request**

Assert ncc\_active\_req to request the return from the bus master stop or system stop.

### **Activation Complete**

The transition to this state is made when a return from the bus master stop or system stop is completed. At this time, assert ncc\_active\_ack to notify the outside about the completion.

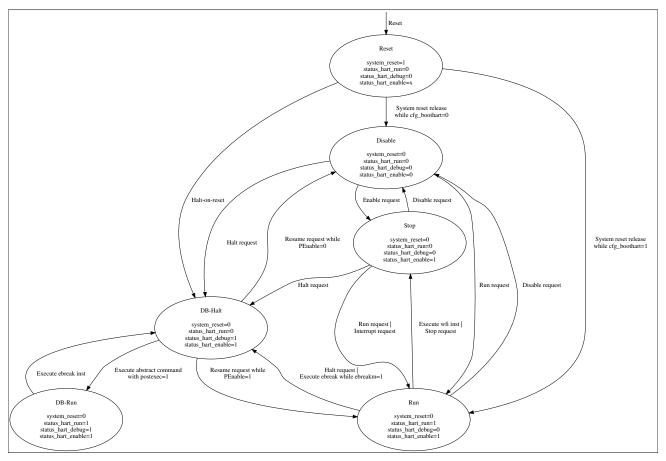

# 3.3.2. Core-level states

Core-level states are the states that the core (NS31A Core Complex) has. Core-level states are controlled together with System-level states.

Figure 5. Core-level states transition diagram

#### Reset

The reset state of a core. No functions of the core can be used.

#### **Core Active**

The active state of a core. All functions of the core can be used.

# **Core Inactive**

The inactive state of a core. Program execution functions of the hart in the core are stopped, and the bus master function is also stopped.

If there is a state such as Master Stop where resources in NS31A can be accessed, it is possible to access a register in a core.

The following shows conditions for each state transition.

#### Power-on Reset or System Reset

Perform the reset according to the procedures described in Section 5.2.1 and Section 5.2.2.

#### System Reset Release

Release the reset according to the procedure described in Section 5.2.2.

# **Master Stop Complete**

The transition to this state is made when the operation of the hart in the core has been stopped via ncc\_mststop\_req.

# **Master Activation Complete**

The transition to this state is made when the operation of the hart in the core has been resumed via ncc\_active\_req.

#### 3.3.3. Hart-level states

Hart-level states are the states of the hart included in the core.

These states indicate execution states, which are independent from the privilege mode of the hart.

Hart-level states are controlled according to state transition requests from the outside of NS31A or CMU, debug control requests from DBG, the execution of instructions, etc.

Figure 6. Hart-level state transition diagram

### Reset

This is the initial state entered when Power-on Reset or System Reset is performed.

#### Stop

The state where the execution of a program is stopped. The transition to the Run state is made when an interrupt is acknowledged.

#### Run

The state where a program is in execution.

#### Disable

The state where the hart is disabled. The execution of a program is stopped, and interrupt requests are ignored.

#### DB-Halt

This is one of the states in the Debug Mode. In this state, the execution of a program is temporarily stopped for debugging.

#### DB-Run

This is one of the states in the Debug Mode. In this state, a debug program is being executed.

- In a state other than Reset, it is possible to access the memory-mapped register of the hart, regardless of whether the program is running or stopped.

- If any exception shown in Table 16 or Table 17 (excluding the reset and interrupts) occurs while the Abstract command is executed (DB-Run), the following behavior occurs.

- 0x3 is set in the cmderr bit of the abstractcs register.

- Branching to the exception vector address is not performed, and the exception-related CSRs (mcause, mepc, mtval, mstatus, mncause, mnepc, and mnstatus) and the exception-related memory mapped register (meecaddr) are not updated.

- Transition to the DB-Halt state is made without executing the subsequent instruction of the debug program.

The following describes each state transition in detail.

#### System reset release

Release the reset according to the procedure described in Section 5.2.2.

The destination state of a state transition changes according to the setting of the external pin cfg\_boothart. However, if a Halt request operation is performed during System Reset, the transition to the DB-Halt state, not a normal execution state, is made as a Halt-on-reset.

#### Halt-on-reset

Request Halt during System Reset by using haltreq or Interlock Halt, and then release the reset according to the procedure described in Section 5.2.2.

In PEnable of mhtenable, the value of cfg\_boothart before transition is saved.

## Run request

Assert ncc\_runhart, and set 1 in RUN of mhtstatus or 1 in HARTRUN.

#### Stop request

Set 0 in RUN of mhtstatus.

#### Disable request

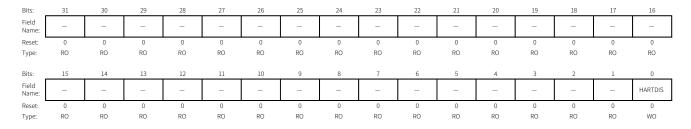

Set 0 in Enable of mhtenable or 1 in HARTDIS.

#### **Enable request**

Set 1 in Enable of mhtenable.

## Halt request

Request Halt by using haltreq of the Debug Module Control Register or Interlock Halt.

At this time, Enable of mhtenable becomes 1, and in PEnable of mhtenable, the value of Enable of mhtenable before transition is saved.

#### Resume request

Request Resume by using resumered of the Debug Module Control Register or Interlock Halt.

At this time, the destination state of a state transition changes according to the value of PEnable of mhtenable.

## Interrupt request

Generate an interrupt request described in Section 3.5. At this time, the state transition occurs regardless of the value of mstatus.MIE.

Note, however, that the state transition does not occur if the interrupt is disabled by mie. In addition, for the External Interrupt, the state transition occurs only if the corresponding interrupt is enabled in eihenN and the priority of the requested interrupt is higher than the priority that is set in eihth.

#### Execute wfi inst

Execute the wfi instruction.

#### **Execute ebreak**

Execute the ebreak instruction. When the state is Run, the state transition occurs only if ebreakm of dcsr is 1 in M-mode or ebreaku of dcsr is 1 in U-mode.

#### Execute abstract command with postexec=1

Set 1 in postexec of the Abstract Command Register, and execute the Abstract Command.

Even when the hart is in the DB-Run state, a System-level state can transition to Master Stop or System Stop. In this case, the execution of the debug program is stopped.

# 3.4. Exceptions

This section describes exceptions supported by NS31A.

An exception is an event that forces the running program to branch to another program. An interrupt is handled as a type of exception. In NS31A, a program that branches due to an exception is run in the M-mode.

In addition to exceptions defined in the RISC-V Priv. Arch. specifications (see Reference Documents for the revision no.), NS31A supports some unique exceptions that are defined according to hardware specifications.

In privilege modes defined in RISC-V, NS31A supports only the Machine mode and User mode. Therefore, exceptions do not occur in the Supervisor mode.

NS31A does not support Page-Based Virtual-Memory System defined in RISC-V. Therefore, the Page fault exception does not occur.

Table 16 and Table 17 show the list of exceptions supported by NS31A.

Table 16. Exception List

|    | ception<br>ode (mcause) | •                                               |           | escription Type Vec                                           |           | mtval               | mstatus     |     |     | meeca<br>ddr |

|----|-------------------------|-------------------------------------------------|-----------|---------------------------------------------------------------|-----------|---------------------|-------------|-----|-----|--------------|

| 31 | 30:0                    |                                                 |           |                                                               |           |                     | mpie        | mie | mpp |              |

| 0  | 0000_0000h              | Reset                                           | -         | resetvec                                                      | Unknown   | Unknown             | 0           | 0   | 0   | 0h           |

| 0  | 0000_0000h              | Instruction address<br>misaligned <sup>*1</sup> | Exception | mtvec                                                         | currentPC | Access address      | current mie | 0   | *3  | s*2          |

| 0  | 0000_0001h              | Instruction access fault                        | Exception | mtvec                                                         | currentPC | Fetch address       | current mie | 0   | *3  | s*2          |

| 0  | 0000_0002h              | Illegal instruction                             | Exception | mtvec                                                         | currentPC | Instruction<br>Code | current mie | 0   | *3  | s*2          |

| 0  | 0000_0003h              | Breakpoint                                      | Exception | mtvec                                                         | currentPC | 0h                  | current mie | 0   | *3  | s*2          |

| 0  | 0000_0004h              | Load address misaligned                         | Exception | mtvec                                                         | currentPC | Access address      | current mie | 0   | *3  | s*2          |

| 0  | 0000_0005h              | Load access fault                               | Exception | mtvec                                                         | currentPC | Access address      | current mie | 0   | *3  | s*2          |

| 0  | 0000_0006h              | Store/AMO address misaligned                    | Exception | mtvec                                                         | currentPC | Access address      | current mie | 0   | *3  | s*2          |

| 0  | 0000_0007h              | Store/AMO access fault                          | Exception | mtvec                                                         | currentPC | Access address      | current mie | 0   | *3  | s*2          |

| 0  | 0000_0008h              | Environment call from U-mode                    | Exception | mtvec                                                         | currentPC | 0h                  | current mie | 0   | 0   | s*2          |

| 0  | 0000_000Bh              | Environment call from M-mode                    | Exception | mtvec                                                         | currentPC | 0h                  | current mie | 0   | 3   | S*2          |

| 1  | 0000_0003h              | Software interrupt                              | Interrupt | mtvec[0]=0: mtvec<br>mtvec[0]=1: mtvec <sup>*4</sup> +<br>0Ch | nextPC    | 0h                  | current mie | 0   | *3  | s*2          |

| 1  | 0000_0007h              | Timer interrupt                                 | Interrupt | mtvec[0]=0: mtvec<br>mtvec[0]=1: mtvec*4 +<br>1Ch             | nextPC    | 0h                  | current mie | 0   | *3  | s*2          |

| 1  | 0000_000Bh              | External interrupt                              | Interrupt | mtvec[0]=0: mtvec<br>mtvec[0]=1: mtvec <sup>*4</sup> +<br>2Ch | nextPC    | 0h                  | current mie | 0   | *3  | s*2          |

| 1  | 0000_0013h              | Error interrupt                                 | Interrupt | mtvec[0]=0: mtvec<br>mtvec[0]=1: mtvec <sup>*4</sup> +<br>4Ch | nextPC    | 0h                  | current mie | 0   | *3  | s*2          |

<sup>\*1</sup> When P\_RV32C is 1, Instruction address misaligned exceptions do not occur.

- \*2 Values do not change before and after exceptions.

- \*3 Depends on the mode in which the exception occurs. (M-mode: 3, U-mode: 0)

- \*4 When mtvec[0] is 1 (Vectored mode), mtvec[6:2] is ignored. For details of the registers, see Section 3.7.2.2.4.

Table 17. Exception List (NMI)

|    | ception Code<br>ncause) | Description                             | scription Type Vec |          | mnepc  | mtval | mnstatus |     | meecad<br>dr      |

|----|-------------------------|-----------------------------------------|--------------------|----------|--------|-------|----------|-----|-------------------|

| 31 | 30:0                    |                                         |                    |          |        |       | nmi      | mnp |                   |

|    |                         |                                         |                    |          |        |       | е        | p   |                   |

| 1  | 0000_0002h              | External NMI                            | NMI                | nmivec*1 | nextPC | s*2   | 0        | *3  | s*2               |

| 1  | 0000_0003h              | Error NMI                               | NMI                | nmivec*1 | nextPC | s*2   | 0        | *3  | s*2               |

| 1  | 0000_0003h              | Fetch Bus error NMI                     | NMI                | nmivec*1 | nextPC | s*2   | 0        | *3  | s*2               |

| 1  | 0000_0003h              | Non-blocking store/AMO bus error<br>NMI | NMI                | nmivec*1 | nextPC | s*2   | 0        | *3  | Access<br>address |

| 1  | 0000_0003h              | Non-blocking load bus error NMI         | NMI                | nmivec*1 | nextPC | s*2   | 0        | *3  | Access<br>address |

<sup>\*1</sup> Set by using the INITNMIVEC register of the CMU. For details of the registers, see Section 6.2.

<sup>\*3</sup> Depends on the mode in which the exception occurs. (M-mode: 3, U-mode:0)

In NS31A, for an exception due to the RV32F (access to the floating-point register) instruction, an exception of a type similar to another instruction type (such as RV32I) occurs.

<sup>\*2</sup> Values do not change before and after exceptions.

# 3.4.1. NS31A unique exception list

The following are exceptions that are uniquely defined for NS31A.

External NMI

NMI that is generated when the external input signal int\_extnmi is asserted.

The detection method is edge.

Error NMI

NMI notified as the Error NMI Request directly from the outside of NS31A via the int\_errnmi pin.

The detection method is edge.

• Error Interrupt

$Interrupt\ notified\ as\ the\ Error\ Interrupt\ Request\ directly\ from\ the\ outside\ of\ NS31A\ via\ the\ int\_errint\ pin.$

The detection method is Level.

· Fetch Bus error NMI

NMI notified if a fatal error occurs due to instruction fetch.

Fatal errors include ECC 2-bit errors and multi-hit errors that occur due to an instruction cache, in addition to bus transaction response errors.

• Non-blocking Store/AMO Bus error NMI

NMI notified if a fatal error occurs when the RV32I Store, RV32C Store, RV32F Store, or RV32A AMO/SC instruction is executed.

In the AXI configuration, fatal errors include ECC 2-bit errors that occur in local memory, in addition to bus transaction response errors.

Non-blocking Load Bus error NMI

NMI notified if a fatal error occurs when the RV32I Load, RV32C Load, RV32F Load, or RV32A LR instruction is executed.

In the AXI configuration, fatal errors include ECC 2-bit errors that occur in local memory, in addition to bus transaction response errors.

Of the exceptions caused by Load/Store/AMO instruction execution in NS31A, Non-blocking NMI occurs asynchronously.

Due to this, an exception other than the Non-blocking NMI may be detected before a Non-blocking NMI that occurred earlier is detected.

In this case, the address stored in mnepc and the mode stored in mnstatus MNPP due to the occurrence of a Non-blocking NMI are not the address and mode of the instruction that caused the NMI to occur but the value of nextPC and the mode at the instant the NMI occurrence was detected.

Local memory and instruction cache ECC 2-bit errors and instruction cache multi-hit errors are usually classified as Hardware Errors, but in NS31A, they are handled as NMIs like bus errors, and the same code (80000003h) is allocated as the value of mncause when they occur.

# 3.4.2. Exception priority

Table 18 lists the priority of exceptions in descending order.

Table 18. Exception Priority

| m[n]cause                | Category              | Description                            |

|--------------------------|-----------------------|----------------------------------------|

| 0000_0000h               | Async                 | Reset                                  |

| 8000_0002h <sup>*1</sup> | Async NMI             | External NMI                           |

| 8000_0003h <sup>*1</sup> | _                     | Error NMI                              |

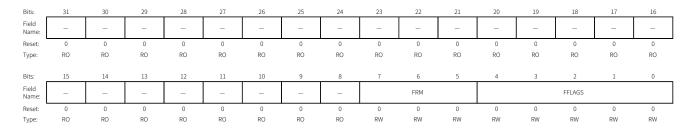

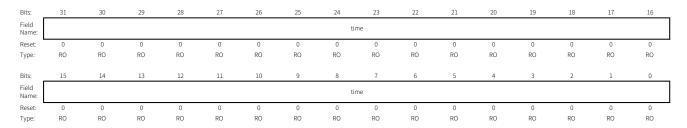

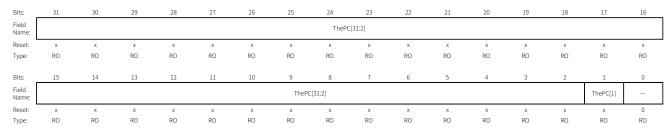

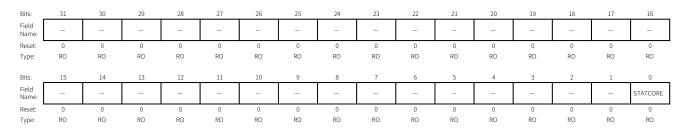

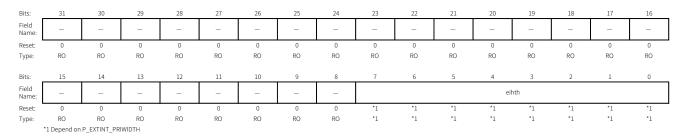

| 8000_0003h*1             | _                     | Non-blocking store bus error NMI       |