-

RISC-V 32bit General Purpose Tiny Core

-

ISO26262:2018 ASIL D compliant SEooC IP

-

RISC-V Solution by Collaborating with Partners

RISC-V 32bit General Purpose Tiny Core

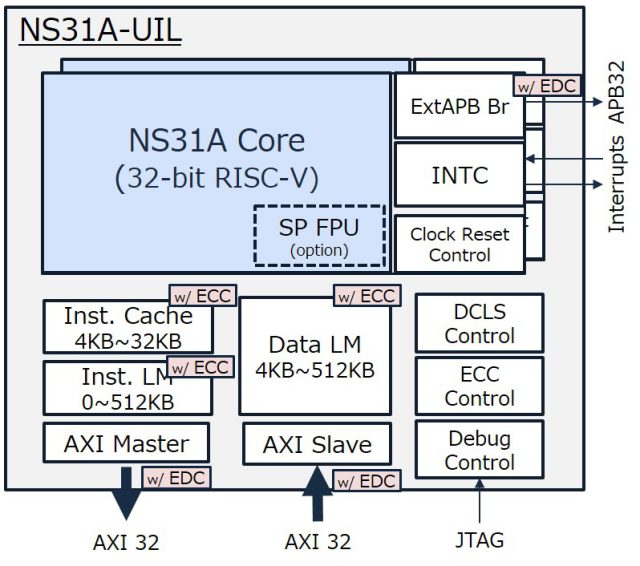

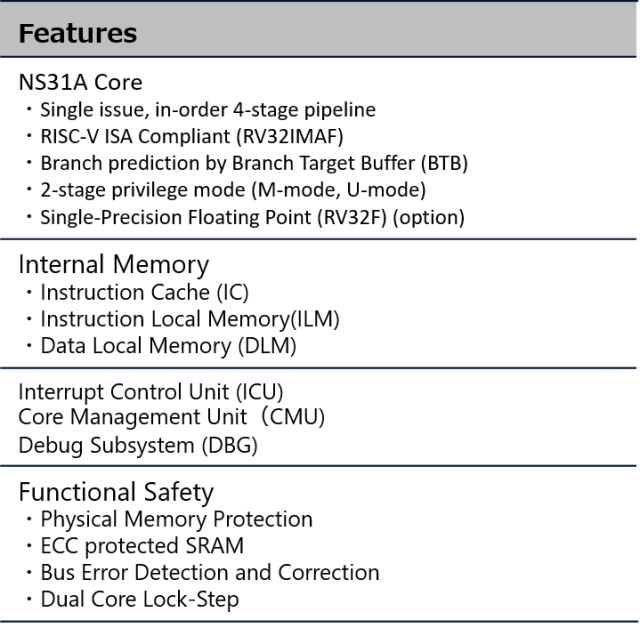

The NS31A is a general-purpose CPU with a single-issue, in-order 4-stage pipeline that uses a 32bits RISC-V ISA (RV32IMAF). It supports ISO 26262 ASIL D functional safety mechanism required for automotive applications, and also supports a privileged mode which required AUTOSAR Platform. NS31A is a highly efficient general-purpose CPU that is ideal for controlling various embedded systems, including automotive applications.

ISO26262:2018 ASIL D compliant SEooC IP

The NS31A has integrated hardware safety features including error correction code (ECC : Error-Correcting Code) for memories, dual-core lockstep architecture for logics, bus protocol violations detection (EDC : Error Detection and Correction), These features enable this processor to meet ASIL D safety requirements without the need to add any external special safety mechanism.

RISC-V Solution by Collaborating with Partners

The OSS based software development tools are available on NS31A. For functional safety development, “IAR Embedded Workbench for RISC-V” made by IAR Systems will support the NS31A as a standard feature.

About “IAR Embedded Workbench for RISC-V”

https://www.iar.com/products/architectures/risc-v/iar-embedded-workbench-for-risc-v/

– – – –

NS31A User Manual download is here